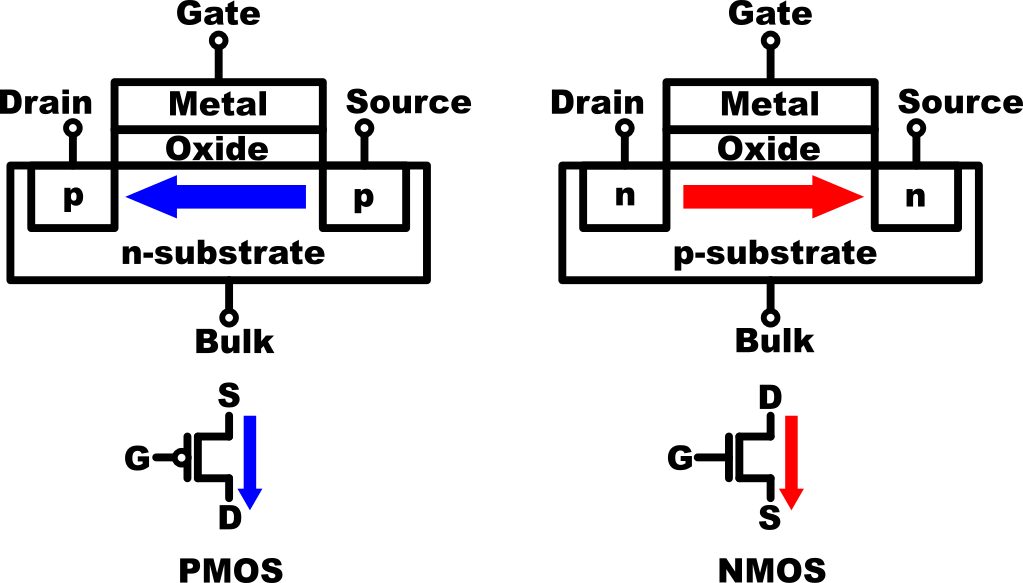

MOSFET (Metal Oxide Semiconductor Field Effect Transistor) devices are important building blocks in modern circuits. MOSFET devices can be classified into two types; PMOS which uses holes and NMOS which uses electrons as carriers. Although they may be different from device standpoint, most of the time, they are used in the same way inside a circuit.

Strictly speaking, MOSFET devices have 4 terminals; source(S), drain(D), gate(G),and bulk(B). However, bulk(B) voltage is usually constant and does not contribute to the overall circuit operation*. Thus, when the purpose of a schematic is to explain the circuit operation, MOSFET devices are often represented as 3-terminal devices by omitting the bulk terminal in the schematic.

* Bulk (B) voltage can affect the threshold voltage of the MOSFET. During circuit design process, bulk voltage of each device has to be chosen appropriately.

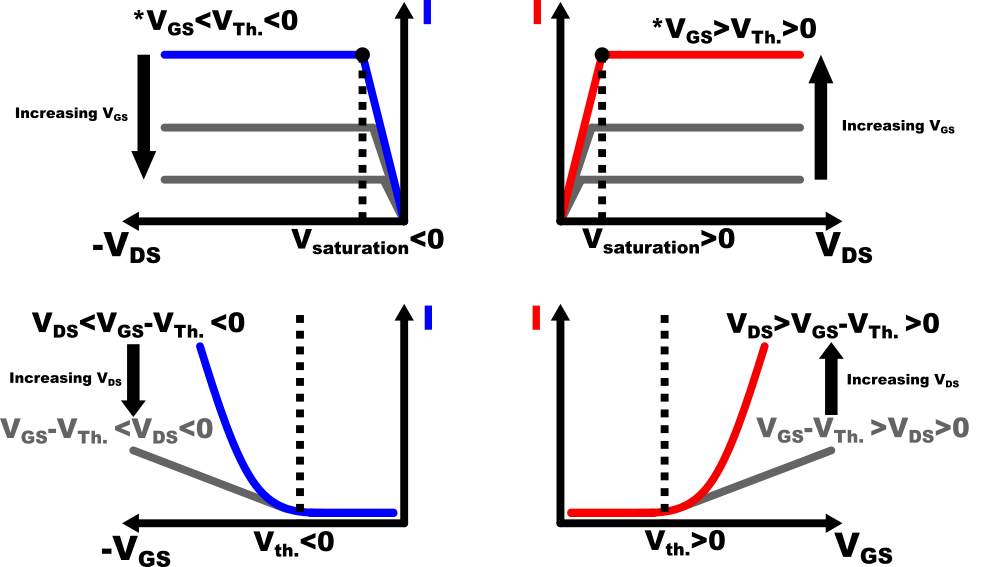

MOSFET, in its essence is a voltage controlled current source. The device takes 3 voltage values (gate,drain,source) as inputs and outputs current whose value is calculated from those 3 inputs. The current characteristic of MOSFET devices are summarized in Fig.2 below.

From the figure, we can see that PMOS and NMOS have fundamentally the same current characteristic.Their difference is only in how they are biased. In PMOS, \( V_S \geq V_G \geq V_D \), thus it is biased with negative voltage relative to its source. In NMOS on the other hand, \( V_S \leq V_G \leq V_D \), thus it is biased with positive voltage relative to its source.

Understanding Fig.1, including how they change under different bias conditions is an important step to intuitively understanding circuit operations. Most circuit operations can be described by changes in these graphs. Several key takeaways from the figure are listed below.

- Current only flows when Gate(G) voltage is past a certain threshold \( V_{th.}\). i.e. \( |V_{GS}| \geq |V_{Th.}| \)

- Decreasing or increasing drain(D) voltage past \( V_{saturation}=V_{GS}-V_{Th.}\) will not change the current value. i.e. \(I=constant\) when \(|V_{DS}| \geq |V_{saturation}| \)

- PMOS drain(D) and gate(G) are biased negatively.Thus, increasing their voltages will \(decrease \) the current.

- NMOS drain(D) and gate(G) are biased positively.Thus, increasing their voltages will \(increase \) the current.